📌 Key Takeaways

A single slip in your supplier timeline can cascade into missed compliance windows, packaging rework, and warranty exposure that far exceeds the original delay.

- Gates Are Artifacts, Not Meetings: A timeline holds when each phase closes with documented evidence—test reports, signed-off samples, and acceptance matrices—not calendar events or status updates.

- Buffers Belong at Risk Points: Allocate schedule slack where delays predictably occur—tool re-cuts, compliance lab bookings, and early production shipments—rather than spreading it evenly across phases.

- Dependencies Must Be Visible: Map firmware releases, tooling milestones, compliance slots, and supply commitments in a single source so one change immediately reveals downstream impacts.

- Golden Sample Criteria Anchor Everything: Define acceptance thresholds before tooling kickoff; this matrix locks packaging claims, guides compliance testing, and prevents negotiation at gates.

- Change Control Protects the Plan: Post-freeze design changes require documented impact analysis, regression testing, and approval before proceeding—firmware updates aren’t exempt from governance.

Prepared gates, explicit buffers, and artifact-based acceptance transform hope into accountability. Program owners, procurement teams, and quality managers will find the framework here, preparing them for the phase-by-phase implementation details that follow.

An RFQ-to-SOP timeline for OEM amplifier programs is the planned sequence from initial Request for Quotation through Start of Production. Think of it like a pit crew’s choreographed routine—every station knows its job, the hand-offs are practiced, and the tools are staged in sequence. When one step bleeds into the next without clear completion criteria, the entire schedule unravels.

Consider a brand launching a private-label power amplifier. The industrial design freezes on schedule, tooling kicks off, and then—three weeks before the pilot run—thermal testing reveals that the heatsink geometry won’t meet sustained-load requirements. The supplier proposes a re-cut, which pushes the golden sample gate by four weeks. Marketing has already locked packaging claims. Compliance lab slots are booked. The launch window closes.

This happens when gates exist as calendar events rather than artifact-based checkpoints. A gated plan with explicit buffers and acceptance criteria transforms hope into accountability.

“Timelines hold when gates are artifacts, not meetings.”

Why OEM Amplifier Timelines Slip

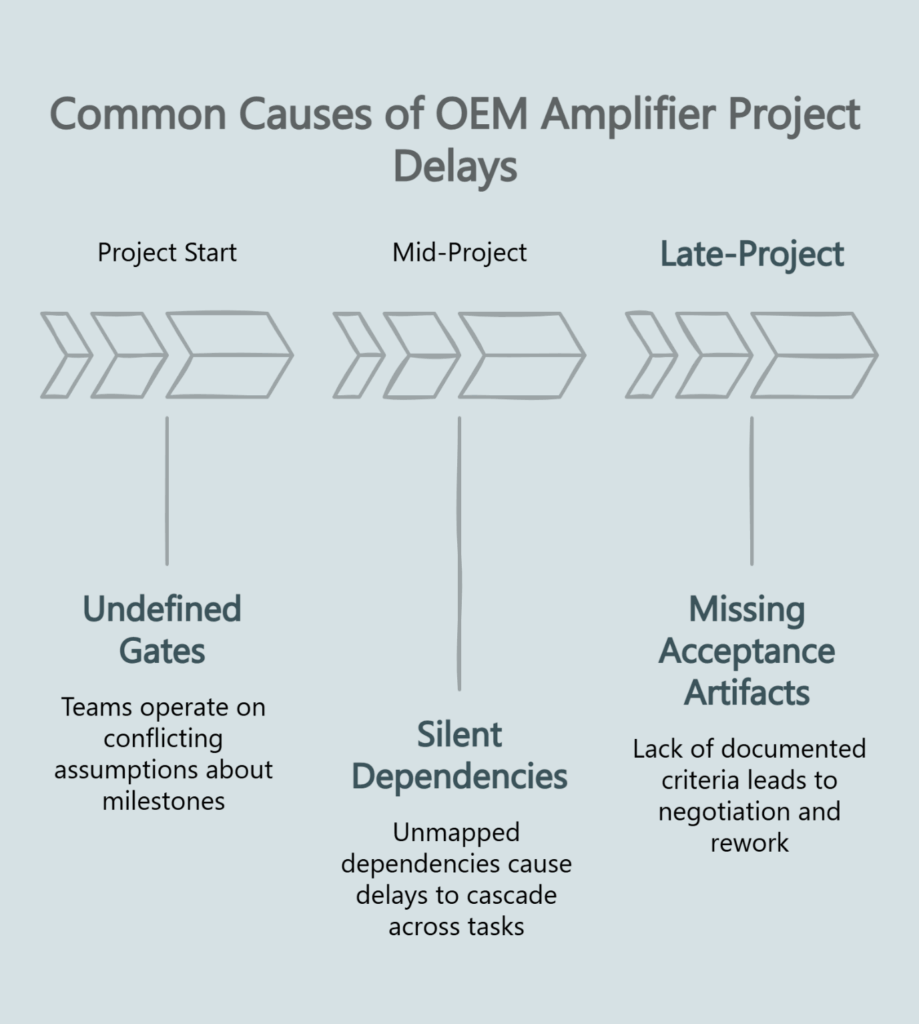

Timelines derail when three conditions converge: undefined gates, silent dependencies, and missing acceptance artifacts.

Without defined gates, teams operate on assumptions. One group believes “design freeze” means the schematic is locked. Another assumes it includes the BOM, the firmware baseline, and the test plan. A supplier begins tooling while DFM feedback is still pending. When the electrical team requests a layout change to address EMC risk, it’s treated as scope creep rather than a necessary correction caught at the wrong phase.

Silent dependencies create compounding delays. Compliance testing depends on finalized packaging claims, which depend on golden sample sign-off, which depends on tooling completion and thermal validation. Firmware changes require regression testing before the pilot run can proceed. When these chains aren’t mapped and calendarized, a single slip cascades across the schedule. The team discovers the coupling only when it’s too late to recover.

Missing acceptance artifacts leave room for interpretation. A “golden sample” without documented acceptance criteria becomes a negotiation at the gate. What constitutes passing thermal performance? Which test conditions matter? If the supplier delivers a unit that measures within specification under one load profile but drifts under another, is the gate cleared or not? Ambiguity breeds rework.

The Stakes: Slips Compound Risk and Cost

A delayed timeline doesn’t just push the launch date—it compresses the window for catching problems that matter.

When the golden sample arrives late, packaging and compliance work proceed in parallel rather than sequence. Claims get locked before thermal data confirms sustained-load behavior. Compliance labs are booked months in advance; missing a slot can mean waiting for the next available window. If a certification test reveals an issue that requires a board revision, the schedule absorbs both the re-test cycle and the lost lab time.

Compressed schedules also increase warranty exposure. Pilot runs exist to surface yield issues, stress-test the supply chain, and validate the control plan under production conditions. Rushing through this phase to recover lost time means the first mass-production shipments become the real pilot. Early field failures are expensive—not just in replacement cost, but in brand reputation and the engineering time required to diagnose problems that should have been caught during a properly executed ramp.

Picture a scenario where variance in a golden sample’s distortion performance goes unnoticed because the sample was approved under time pressure. The issue only surfaces after the first production batch ships, requiring a field retrofit or product recall. That’s the cost of treating gates as formalities rather than decision points.

The Solution: A Gated RFQ-to-SOP Model

A timeline holds when each phase concludes with a documented gate: required artifacts, acceptance criteria, ownership, dependency checks, and explicit buffers. This approach adapts PPAP-like gating concepts from automotive manufacturing to audio amplifier programs without requiring full automotive ritual. Here’s how to structure it.

Phase 0: RFQ Pack Finalization

The gate requires a complete RFQ package: product requirements document, target markets and regulatory scope, test philosophy, and MOQ/lead-time expectations. The supplier must acknowledge all elements and surface any gaps or contradictions before proceeding.

Owner: Program manager and procurement.

Dependency: None—this is the starting anchor.

Buffer: Three to five business days for supplier Q&A and internal alignment.

Acceptance: Signed acknowledgment from the supplier that the RFQ is complete and understood.

Phase 1: Supplier Qualification and QMS/DFM Review

The gate requires evidence of QMS maturity, such as ISO 9001 certification or equivalent quality management documentation, CAPA history for similar products, and a preliminary DFM review covering thermal management and EMC layout. An early compliance matrix identifies which certifications apply and their typical lead times.

Owner: Quality and engineering.

Dependency: RFQ pack finalized.

Buffer: One week for counter-DFM questions and clarifications.

Acceptance: Signed DFM report and compliance matrix with no unresolved high-risk items.

Phase 2: Design Freeze and Pre-Tooling

The gate requires BOM version 1.x, mechanical drawings, firmware baseline (with version control), and an outline of acceptance test procedures. Change-control rules take effect: any post-freeze changes require documented justification, impact assessment, and regression testing.

Owner: Engineering lead.

Dependency: DFM closure.

Buffer: Cool-off period of three to five days between freeze and tooling kickoff to catch last-minute oversights.

Acceptance: Signed design freeze document with change-control SLA.

Phase 3: Tooling Kickoff (T0) and EVT/DVT Builds

The gate requires a tool plan (cavitation, materials, lead times), defined golden sample criteria (the acceptance matrix for what constitutes a passing unit), thermal performance targets, and pre-compliance test slots booked. Early verification builds (EVT/DVT) validate electrical performance and identify mechanical fit issues before committing to production tooling.

Owner: Supplier (tool shop) and internal engineering.

Dependency: Design freeze.

Buffer: Four weeks for potential tool re-cuts and long-lead component procurement.

Acceptance: Tool first-article inspection report and EVT/DVT test data within specification.

Phase 4: Golden Sample Sign-Off (PPAP-Like Gate)

The gate requires a golden sample measured against the acceptance matrix, complete test reports (electrical, thermal, environmental), material traceability, and process capability data. Packaging claims lock after this gate—no performance specifications may be published until the golden sample passes.

To maintain configuration integrity post-approval, implement ISO 10007 configuration management principles. Any changes to the golden sample configuration after this gate must follow documented change control with impact analysis and regression testing.

Owner: Quality and product management.

Dependency: Tooling completion and thermal validation.

Buffer: One iteration loop (two weeks) for minor adjustments if the first sample reveals edge-case issues.

Acceptance: Signed golden sample approval with traceability documentation.

Phase 5: Pilot Run (Mass Production Readiness)

The gate requires pilot units built at target yield rates, stress and thermal soak testing on pilot samples, RMA process simulation, and firmware regression testing. This phase validates that the manufacturing process can consistently produce units that meet specification.

Owner: Operations and quality.

Dependency: Golden sample approval and compliance test plan locked.

Buffer: Two weeks for capacity ramp and yield troubleshooting.

Acceptance: Pilot summary report showing yield ≥ target, with documented corrective actions for any failures.

For additional context on automated testing strategies that reduce DOA rates without slowing ramp schedules is available in ATE & End-of-Line Testing for Amplifiers: Reducing DOA Without Slowing Ramp.

Phase 6: Compliance and Safety Approvals

The gate requires market-specific test reports, including IEC 62368-1 for audio/video equipment safety and CISPR/EMC standards appropriate to target markets. Labeling proofs and user manuals must also be finalized. Compliance labs are typically booked months in advance based on the Phase 1 compliance matrix; any delays here cascade directly into the SOP date.

Owner: Compliance specialist and supplier.

Dependency: Pilot run completion and packaging finalized.

Buffer: Lab scheduling buffer of four to six weeks to accommodate re-tests or seasonal lab congestion.

Acceptance: Signed compliance certificates and approved label artwork.

Phase 7: Start of Production (SOP)

The gate requires a control plan (IQC/IPQC/FQC procedures), incoming inspection criteria, RMA flow documentation, and serial/lot traceability active. The first two production shipments receive enhanced inspection to catch any process drift that wasn’t visible during the pilot, before relaxing to steady-state quality controls.

Owner: Operations and quality.

Dependency: All prior gates cleared, including compliance.

Buffer: None—this is the delivery milestone. However, enhanced inspection acts as a safety net.

Acceptance: First shipment released with full traceability and no critical defects.

Keeping the Plan True to Schedule

A gated timeline only works if the gates are calendarized and the dependencies are visible.

Schedule gate reviews as fixed calendar events with required attendees (program manager, engineering lead, quality, supplier representative). The review isn’t a status update—it’s a go/no-go decision based on artifact completeness. If artifacts are missing or acceptance criteria aren’t met, the gate doesn’t clear, and downstream work pauses until the issue is resolved.

Maintain a single-source dependency map that tracks firmware release schedules, compliance lab bookings, tooling milestones, and long-lead supply commitments. When a change occurs in one area, the map immediately reveals which downstream activities are affected. This prevents the “surprise” delays that occur when teams operate in isolated workstreams.

Pre-define buffers at risk points rather than distributing slack evenly across the schedule. Tool re-cuts, compliance lab availability, and early production yield variability are predictable risk areas. Allocating buffer time to these specific phases creates resilience without inflating the overall timeline arbitrarily.

Establish change-control service-level agreements post-freeze. If a design change is unavoidable, the SLA defines how quickly the supplier must assess impact, execute the change, and deliver updated test data. This prevents changes from lingering in “pending” status while the rest of the schedule marches forward.

Require test-data visibility throughout the process. The supplier shouldn’t be the sole holder of thermal curves, distortion measurements, or yield reports. Shared access to test data allows your team to spot trends early and intervene before a minor variance becomes a gate-blocking failure.

For programs spanning multiple product categories, align timeline governance across amplifier manufacturing, coaxial speaker, and pro audio OEM platforms to maintain consistency in gate requirements and buffer allocation.

What to Request from the Supplier on Day One

Securing these items at the start sets clear expectations and prevents mid-program scrambles.

- QMS and CAPA evidence: Request ISO 9001 (or equivalent) certification and CAPA logs for similar amplifier programs from the past two years. This reveals how the supplier handles corrective actions and whether quality issues tend to recur.

- DFM package: A preliminary design-for-manufacturing review covering thermal dissipation, PCB layout for EMC, and assembly complexity. This identifies risks before tooling begins. For deeper context on DFM specifications that most affect amplifier yield, see DFM Inputs for Amplifiers: The Eight Specifications That Most Affect Yield.

- Preliminary tool plan: Cavitation strategy, material selection, lead times, and contingency plans for re-cuts. Knowing the tooling schedule upfront prevents optimistic assumptions.

- Golden sample criteria: A draft acceptance matrix defining electrical specs, thermal limits, and environmental stress conditions. This document anchors all subsequent testing and prevents moving goalposts.

- Test-data access: Credentials or a shared portal for viewing real-time test results, yield data, and compliance pre-test outcomes. Transparency reduces negotiation friction at gates.

- Obsolescence notice policy: How far in advance the supplier commits to notifying you of component end-of-life or supply constraints. This protects your ability to manage running changes without scrambling for redesigns.

- Pilot exit metrics: Agreed-upon yield targets, defect rates, and stress-test pass criteria that define when the pilot phase successfully concludes.

To understand the full manufacturing handoff from DFM through production ramp, see Amplifier Manufacturing Services: A DFM-to-Ramp Framework for Reliable On-Time Launches.

Frequently Asked Questions

What’s a realistic place to add buffers without bloating the schedule?

Focus buffers at tool re-cut risk points, compliance lab booking windows, and the first two production shipments under enhanced inspection. These are predictable stress points where delays occur most frequently.

How early should golden sample criteria be defined?

Before tooling kickoff. The criteria anchor acceptance thresholds for all subsequent gates, including packaging claims and compliance testing. Defining them late forces rework.

Do we need PPAP exactly?

Not necessarily. A PPAP-like gate set tailored to audio amplifiers is sufficient as long as artifacts and acceptance criteria are explicit. The principle—documented evidence at each phase—matters more than strict adherence to automotive PPAP procedures.

Where do firmware changes sit in the timeline?

Baseline the firmware at Design Freeze. Any post-freeze changes follow documented change control with regression testing completed before the Pilot Exit Gate. Firmware isn’t exempt from governance.

How do we keep marketing and packaging aligned?

Lock performance claims only after Golden Sample Gate. Include compliance marks and user manuals in the compliance gate checklist to prevent misalignment between what’s advertised and what’s certified.

Disclaimer: This guide is informational and not legal or compliance advice. Always confirm market-specific standards and certification requirements with qualified professionals.

Our Editorial Process

We prioritize accuracy, clarity, and real-world usefulness. Articles are reviewed for structure, terminology consistency, and alignment with our B2B content guidelines before publishing.

About the China Future Sound Insights Team

The China Future Sound Insights Team distills complex manufacturing topics into clear, helpful guides. Reviewed for clarity and accuracy; informational only, not a substitute for professional advice.